CSE 331 Computer Organizations Homework 4

Table of Contents

2 Assignment

Supporeted instructions: lw, sw, j, jal, jr, beq, bne, addn, subn, xorn, andn, orn, ori, lui

But the R-type instructions will execute different than the conventional MIPS. This is why they have ‘n’ at the end (representing new). The new instructions have the same opcode and function fields as the conventional R-type instructions. But the execution is different. For instance:

addn $rd, $rs, $rt

RTL Representation:

$rs <= $rs + $rt if($rs + $rt == 0) $rd <= 1 else if($rs + $rt < 0) $rd <= 2 else $rd <= 3

The data memory size will be 256KB whereas the instruction memory size will be 16KB. Addressing for a 256KB memory only requires 18 bits instead of 32 bits in regular MIPS.

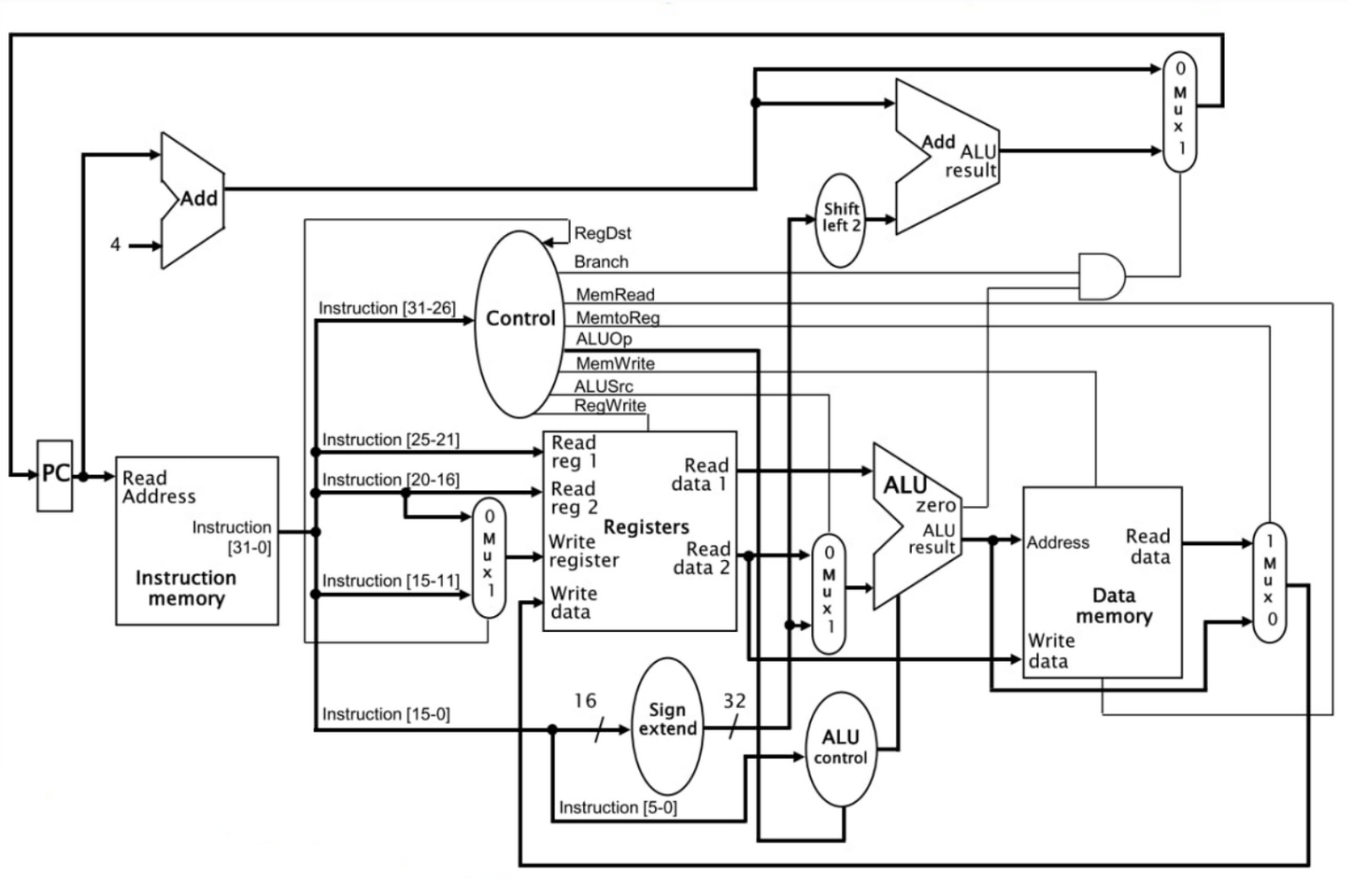

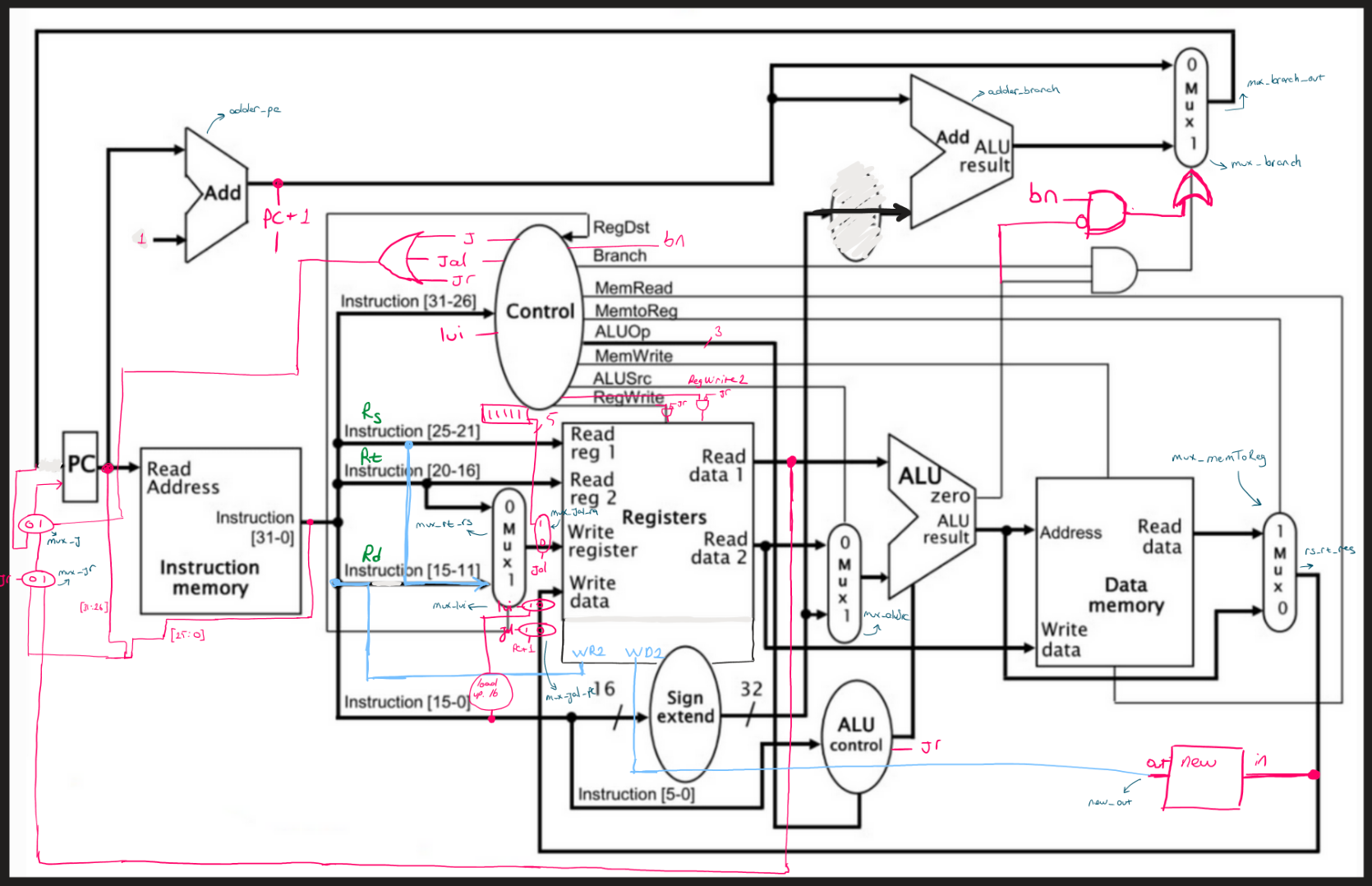

3 Datapath

Updated datapath;

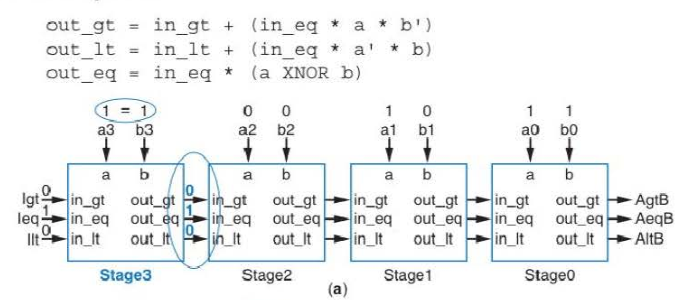

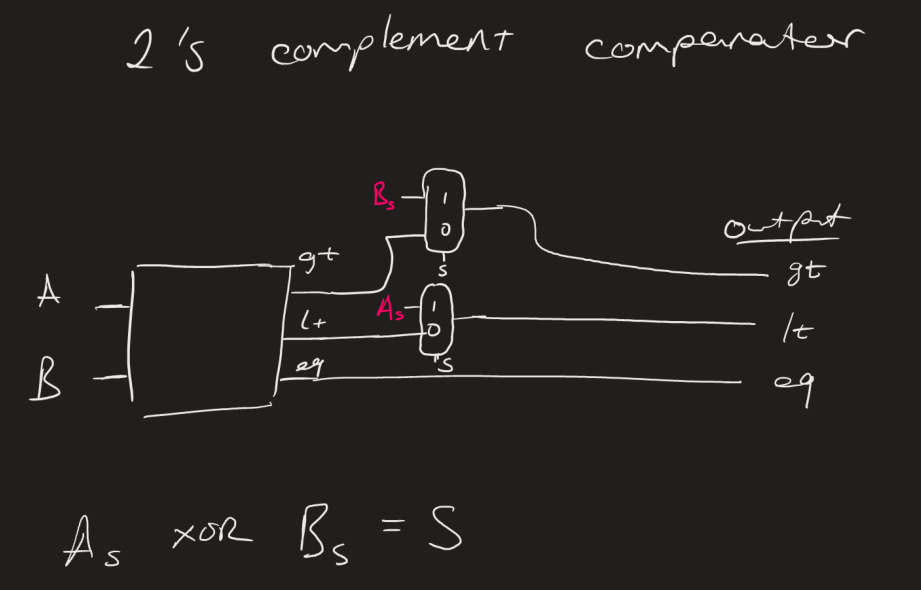

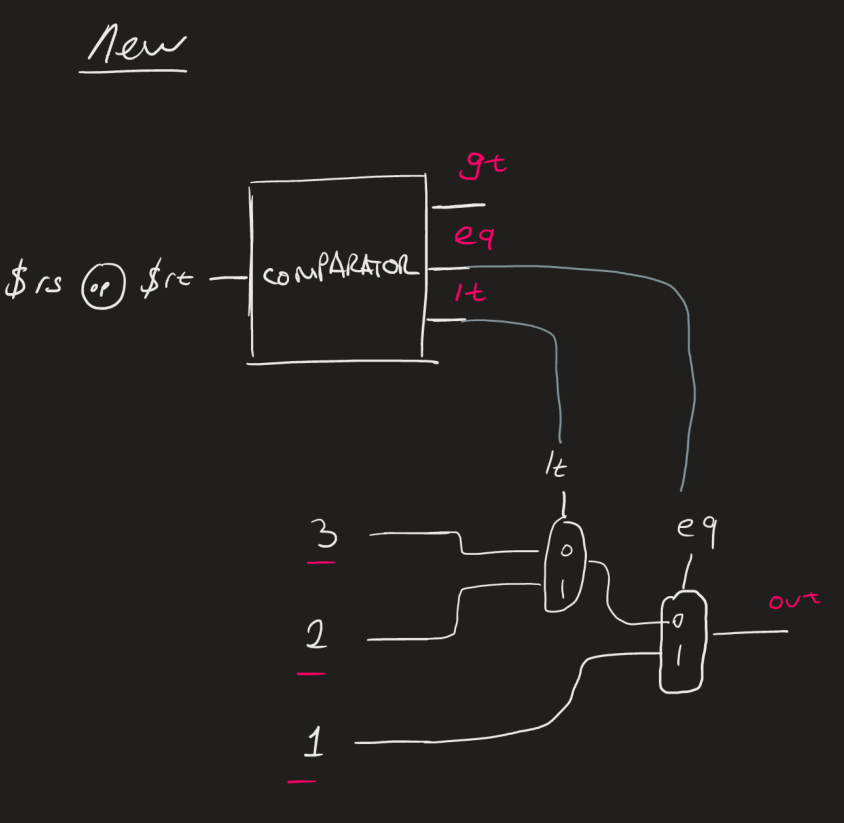

3.1 Comparator

We need 2's complement comparator in order to check the result is greater or less than 0. (for new-type instructions)

- As: sign bit of A

- Bs: sign bit of B

| As | Bs | result |

|---|---|---|

| 0 | 0 | use unsigned comparator |

| 0 | 1 | A > B |

| 1 | 0 | B < A |

| 1 | 1 | use unsigned comparator |

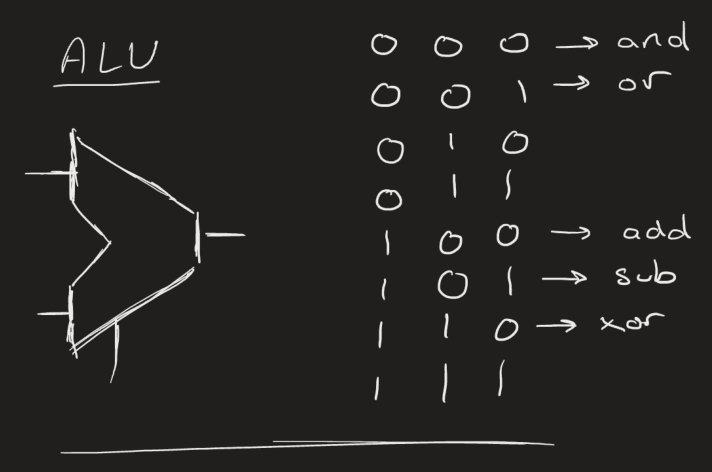

3.2 ALU

In order to perform arithmetic and logical operations we need is ALU. Needed operations are;

- addition

- substraction

- and

- or

- xor

3.3 New block (for addn, subn, xorn, andn, orn)

3.4 ALU control

| ins | aluop1 | aluop0 | f5 | f4 | f3 | f2 | f1 | f0 | c2 | c1 | c0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| lw/sw | 0 | 0 | x | x | x | x | x | x | 1 | 0 | 0 |

| beq/bne | 0 | 1 | x | x | x | x | x | x | 1 | 0 | 1 |

| r/addn | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| r/subn | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| r/andn | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| r/orn | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| r/xorn | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| ori | 1 | 1 | x | x | x | x | x | x | 0 | 0 | 1 |

We don't need to consider f5, f4, f3 since they are same or not important for output.

c2 = o1' + o1 o0' (f0' ( f2' f1' + f2' f1 + f2 f1)) c2 = o1' + o1 o0' (f0' ( f2 f1')') c2 = o1' + o1 o0' (f0' ( f2' + f1)) c2 = o1' + o0' (f0' ( f2' + f1)) c1 = o1 o0' f2 f1 f0' c0 = o1' o0 + o1 o0 + o1 o0' (f2' f1 f0' + f2 f1' f0) c0 = o0 ( o1' + o1) + o1 o0' (f2' f1 f0' + f2 f1' f0) c0 = o0 + o1 o0' (f2' f1 f0' + f2 f1' f0) c0 = o0 + o1 (f2' f1 f0' + f2 f1' f0)

j and jal can not be detected by main control unit, because they are J-type. However jr is R-type, therefore we can only understand it by looking its function field. So ALU-control will have jr output.

- Function field of

jr: 001000 - Since

jris R-type,aluop: 01

For function field, f5 is 1 for all other R-type instructions but jr.

jr = o1 o0'f5'

3.5 Control Unit

| Opcode | 000000 | 100011 | 101011 | 000100 | 000101 | 001101 | 000010 | 000011 | 001111 |

| Instruction type | R-type | lw | sw | beq | bne | ori | j | jal | lui |

| RegDst | 1 | 0 | X | X | X | 0 | X | X | 0 |

| ALUSrc | 0 | 1 | 1 | 0 | 0 | 1 | X | X | X |

| MemtoReg | 0 | 1 | X | X | X | 0 | X | X | X |

| RegWrite | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| RegWrite2 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| MemRead | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| MemWrite | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Branch | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| BranchNot | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| Lui | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Jump | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| Jal | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| AluOp | R-type | Add | Add | Sub | Sub | Or | X | X | X |

| ALUop1 | 1 | 0 | 0 | 0 | 0 | 1 | X | X | X |

| ALUop0 | 0 | 0 | 0 | 1 | 1 | 1 | X | X | X |

RegDst = r-type ALUSrc = lw + sw + ori MemtoReg = lw RegWrite = r-type + lw + ori + jal + lui RegWrite2 = r-type + MemRead = lw MemWrite = sw Branch = beq BranchNot = bne Lui = lui Jump = j Jal = jal ALUop_1 = r-type + ori ALUop_0 = beq + bne + ori

4 Report

I have used behavioural verilog on register block, data memory, instruction memory. Also I have implemented a register for program counter.

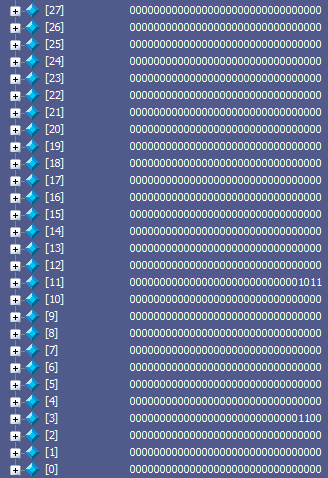

Initally contents off all the registers are 0.

I have run the machine code of the following assembly code and show the results.

.text ori $t1, $0, 8 ori $t2, $0, 5 add $t3, $t2, $t1 add $t3, $t2, $t1 ori $t2, $0, 5 sub $t4, $t2, $t1 sub $t4, $t2, $t1 ori $t2, $0, 7 ori $t1, $0, 11 xor $t3, $t2, $t1 xor $t3, $t4, $t1 sw $t1, 2($t4) sw $t2, ($t3) lw $t5, ($t3) lw $t6, 2($t4) lui $t1, 1 lui $t7, 17 and $t8, $t5, $t6 and $t9, $t2, $t3 or $a0, $t1, $t7 or $a0, $t2, $t3 ori $s0, 1 ori $s1, 1 beq $s0, $s1, label0 ori $s2, 1 ori $s3, 1 label0: ori $s4, 1 ori $s5, 1 ori $s6, 1 ori $s7, 1 ori $s1, 1 bne $s0, $s1, label1 ori $s2, 1 j label1 ori $s0, 2 ori $s1, 2 label1: ori $s2, 2 ori $s3, 2 ori $s4, 2 jal label2 ori $s5, 2 label2: ori $s6, 2 ori $s7, 2 jr $ra

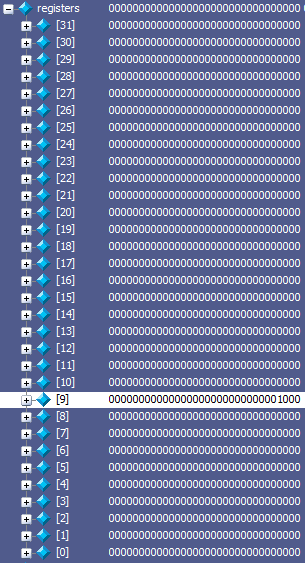

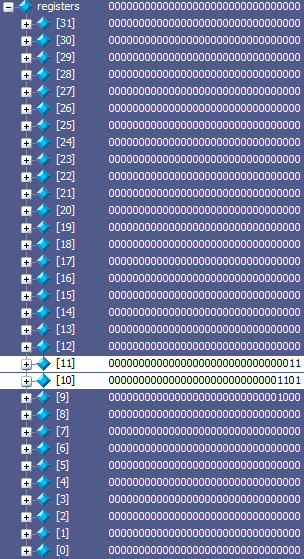

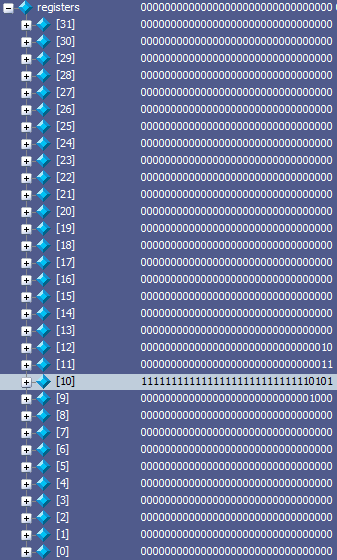

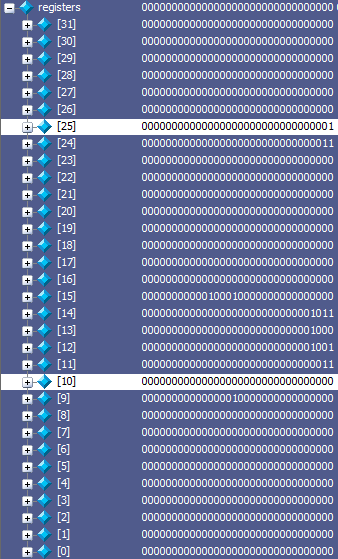

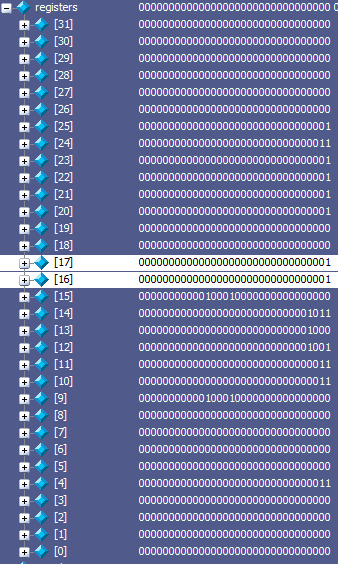

ori $t1, $0, 8

Figure 7: $t1 (9th register) <= ..0000 OR ..1000

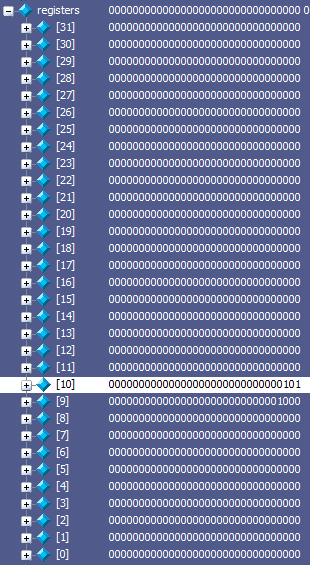

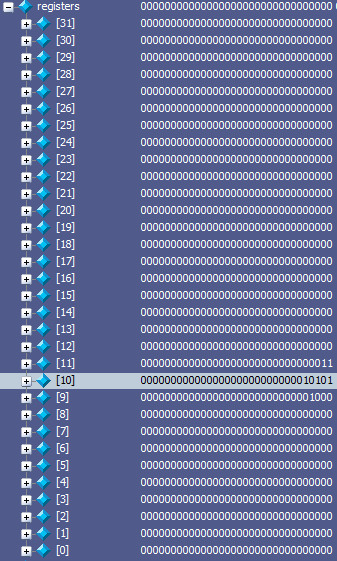

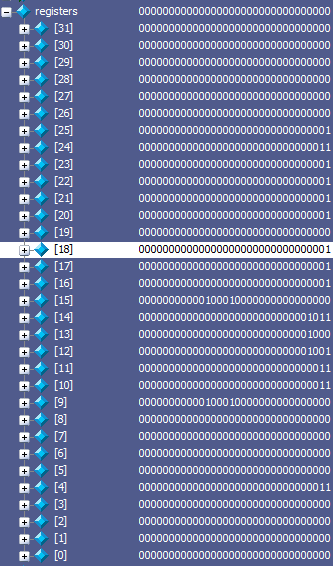

ori $t2, $0, 5

Figure 8: $t2 (10th register) <= ..000 OR ..101

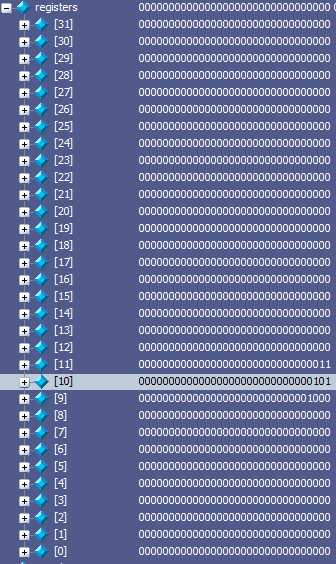

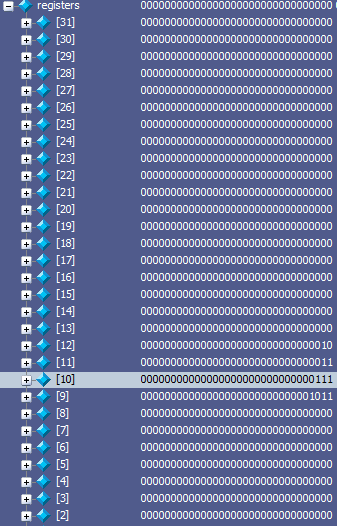

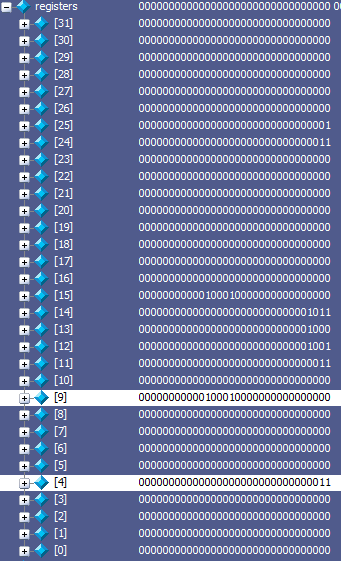

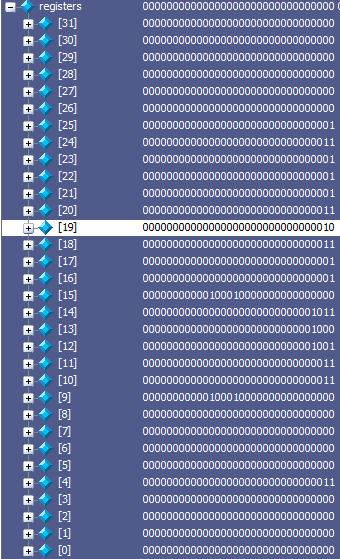

add $t3, $t2, $t1

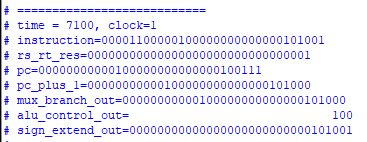

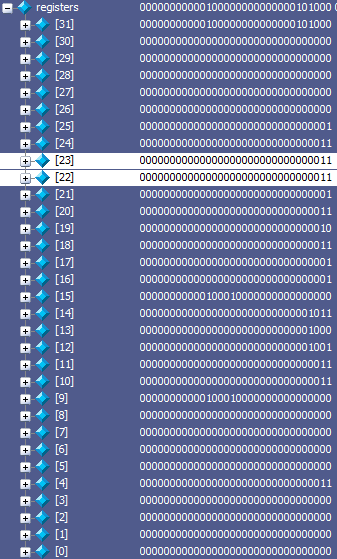

Figure 9: $t2=8+5=13, 13>0, then $t3(rd)=3

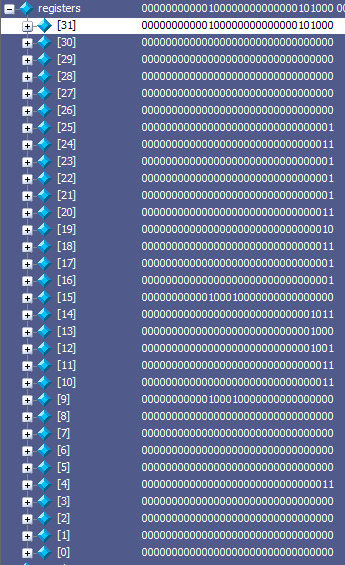

add $t3, $t2, $t1

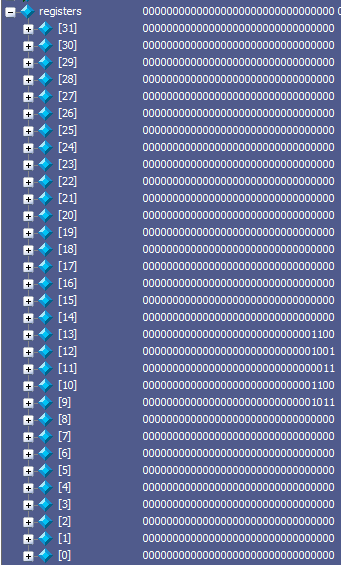

Figure 10: $t2=13+8=21, 21>0 then $t3=3

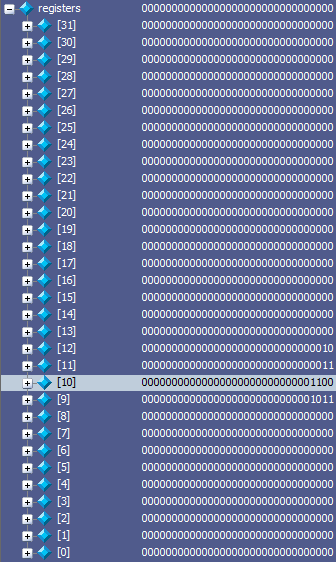

ori $t2, $0, 5

Figure 11: $t2 = 5

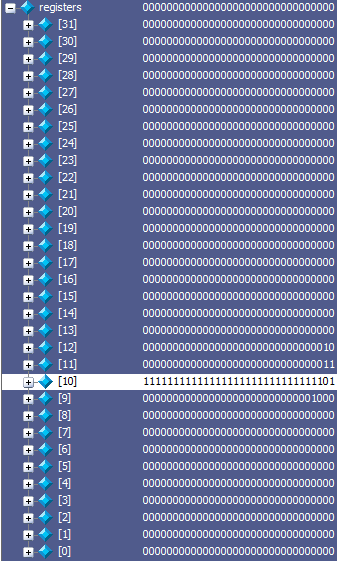

sub $t4, $t2, $t1

Figure 12: $t2=5-8=-3, -3<0 then $t4=2

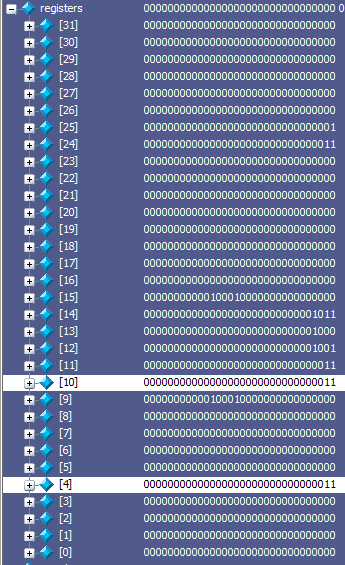

sub $t4, $t2, $t1

Figure 13: $t2=-3-8=-11, $4=2

ori $t2, $0, 7 ori $t1, $0, 11

Figure 14: $t2=7, $t1=11

xor $t3, $t2, $t1

Figure 15: $t2 = 0111 XOR 1011, $t3=2

xor $t3, $t4, $t1

Figure 16: $t4 = 0010 XOR 1011 = 1001, $t3 = 3

sw $t1, 2($t4)

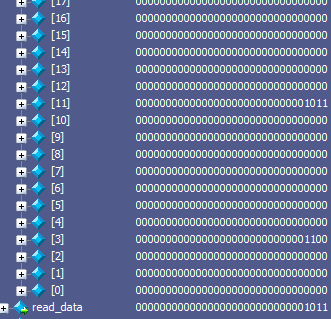

Figure 17: contents of $t4:9, offset=2 address=9+2=11, data = contents of $t1: 1011 (data block)

sw $t2, ($t3)

Figure 18: address:[$t3]=3, data:$t2=1101 (data block)

lw $t5, ($t3)

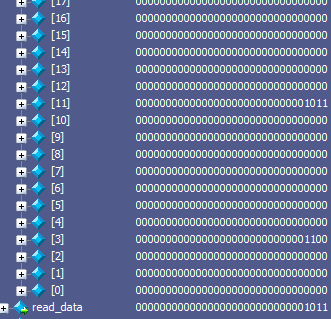

Figure 19: [$t3]=3, contents of 3th line in memory:1100 $t5(13th register)=1100

lw $t6, 2($t4)

Figure 21: [$t4]=9, offset=2, contents of 11th line in memory:1011 $t6(14th register)=1011

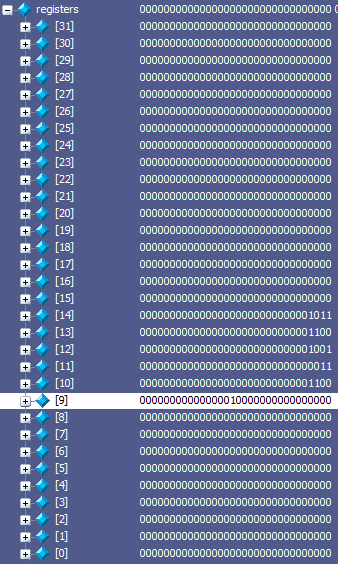

lui $t1, 1

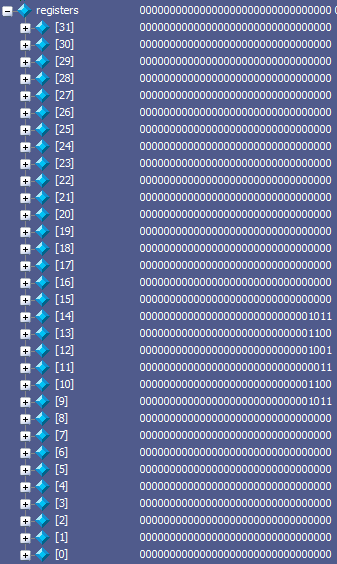

Figure 23: $t1 = {16'b1,16'b0}

lui $t7, 17

Figure 24: $t7 = {16'd17,16d'0}

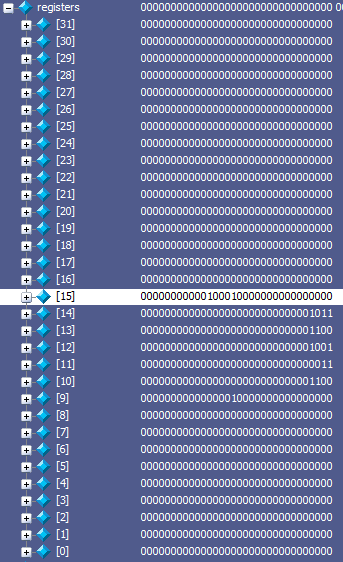

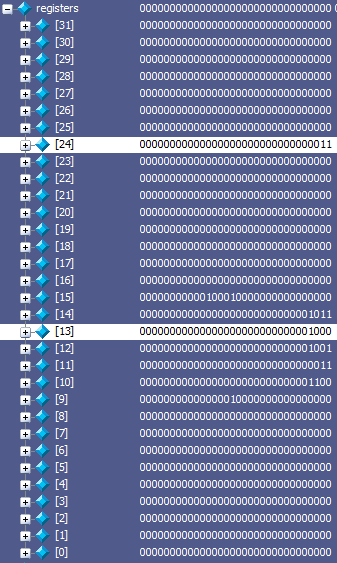

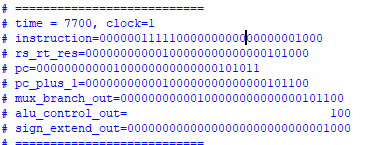

and $t8, $t5, $t6

Figure 25: $t5 = 1100 AND 1011 = 1000, $8(24th register)=3

and $t9, $t2, $t3

Figure 26: $t2 = 1100 AND 0011 = 0000, $t9=1

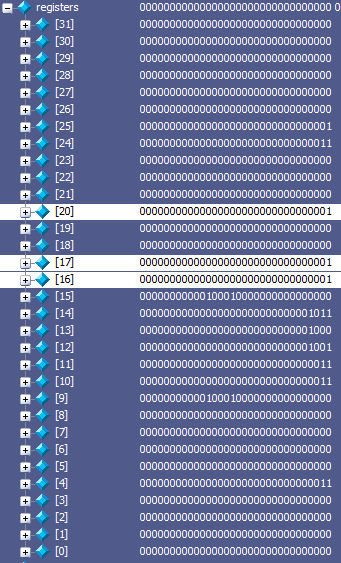

or $a0, $t1, $t7

Figure 27: $t1 = $r1 OR $t7, $a0=1

or $a0, $t2, $t3

Figure 28: $t2 = 0000 OR 0011 = 0011, $a0=3

ori $s0, 1 ori $s1, 1 beq $s0, $s1, label0 ori $s2, 1 ori $s3, 1 label0: ori $s4, 1

Figure 29: s0=1, s1=1, branch to label0, s4=1

ori $s5, 1 ori $s6, 1 ori $s7, 1 ori $s1, 1 bne $s0, $s1, label1 ori $s2, 1

Figure 30: it will not branch since $s0=$s1

Figure 31: s2=1

j label1 ori $s0, 2 # it will not run ori $s1, 2 # it will not run label1: ori $s2, 2

Figure 32: $s2=2 (jumped here)

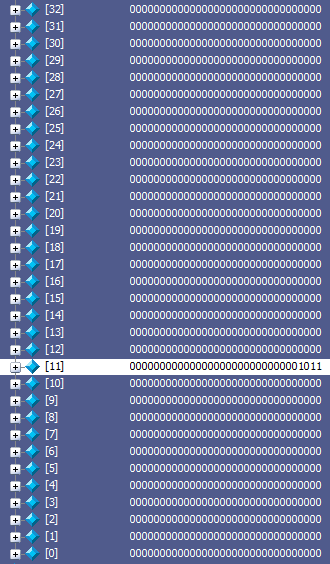

ori $s3, 2 ori $s4, 2 jal label2 ori $s5, 2 label2:

Figure 33: jumped to address and saved $ra the pc

ori $s6, 2 ori $s7, 2

jr $ra

Figure 36: jr $ra, pc will be [$ra]